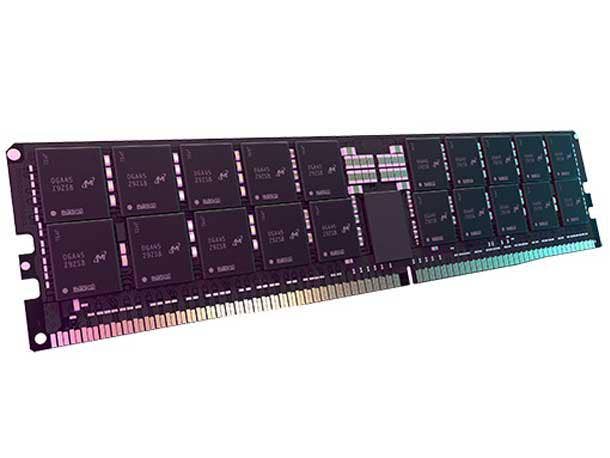

Micron Ships Data Center-Class DDR5, Ready For New AMD EPYC CPUs

‘With these new CPU platforms, we’re making a new generation of memory. Every year, there is new technology. But going from DDR4 to DDR5 is a once-in-a-decade change,’ says Malcom Humphrey, vice president and general manager for Micron’s compute and networking business unit.

Memory manufacturer Micron Technology Thursday said it is shipping its new data center-class DDR5 SDRAM memory in volume and that it is supporting the new AMD new Zen 4 EPYC processors also released on the same day.

A generational change in CPU platforms requires a new generation of memory for optimal performance, and that is what Micron is doing, said Malcom Humphrey, vice president and general manager for the compute and networking business unit of Boise, Idaho-based Micron.

“With these new CPU platforms, we’re making a new generation of memory,” Humphrey told CRN. “Every year, there is new technology. But going from DDR4 to DDR5 is a once-in-a-decade change. And we’re tying it to AMD because it is a package deal. AMD is the first of a couple of enablers launching their new platform with DDR5.”

[Related: AMD CEO Lisa Su: 4th Gen EPYC Genoa Rollout ‘Delivers Leadership’ For Data Center]

The need for a new memory platform comes from continued growth in data and the need for performance to process it, Humphrey said.

“Data is everywhere, and it’s getting bigger,” he said. “In order to turn that data into information, it needs processing. And that requires new CPUs and memory.”

It is important to increase the amount of bandwidth each memory core can process, and with memory, as core count increases and bandwidth per core increases, there’s an increase in performance, Humphrey said.

“But as the core count increases, keeping up with the bandwidth per core is increasingly difficult,” he said. “You have to bring data into and out of cores, and that means bandwidth. We’ve gone from two cores to 64 cores and 96 cores. To keep bandwidth per core flat, we need to increase the DRAM speed and the number of DRAM channels.”

Micron did so with DDR5. It increased the channel count to match AMD EPYC 4’s 12 channels per processor, and increased performance to 4,800 MT/s, or megatransfers per second, compared with DDR4’s 3,200 MT/s. DDR5 can scale to 8,800 MT/s per the specifications of JEDEC, which creates the standards by which microprocessors are built, Humphrey said.

DDR5’s architecture also increases the bandwidth of the bus to two 40-bit channels versus a single 64-bit channel in DDR4, which allows for on-die ECC (error connection code) in addition to system-level ECC, Humphrey said. It also features higher frequency with decision feedback equalization, or DFE, to minimize interference between neighboring pins, and includes on-die performance management to lower power consumption compared with DDR4, he said.

Micron is currently shipping its first two DDR5 products, with additional versions becoming available over the next several quarters.

Micron started its DDR5 production using its current 12-nanometer process technology as opposed to going first on later process nodes, Humphrey said.

“We did what’s right for Micron to get on mature process nodes and to get it right for future nodes,” he said.